# Plan and Implementation of BIST for ISCAS-85 c432 Combinational Circuit

G.Lakshmi Divya<sup>\*1</sup> and N.Praveen Kumar<sup>#2</sup>

<sup>\*</sup>Student, Dept of Electronics and Communication, Nova College of Engineering and Technology, India <sup>#</sup>Asst Professor, Dept of Electronics and Communication, Nova College of Engineering and Technology, India

Abstract— In this proposed method we are test the one combinational circuit. Here this combinational circuit having 36bit input and 7-bit output. ISCAS-85 C432 27-channel interrupt controller is a combinational benchmark circuit. This paper described an on-chip test generation method for functional broadside tests. The hardware was based on the application of primary input sequences initial from a known reachable state, thus using the circuit to produce additional reachable states. Random primary input sequences were changed to avoid repeated synchronization and thus yield varied sets of reachable states. The hardware structure was simple and fixed, and it was tailored to a given circuit only through the following parameters: the length of the LFSR used for producing a random primary input sequence; the length of the primary input sequence; the specific gates used for modifying the random primary input sequence; the particular gate used for selecting applied tests; and the seeds for the LFSR. With the proposed on-chip test generation method, the circuit is used for generate reachable states for the duration of test application. This alleviates the want to compute reachable states offline.

Index Terms—Built-in test generation, functional broadside tests, ROM,, reachable states, transition faults, test pattern generator,ISCAS-85 C432 benchmark circuit.

#### I. INTRODUCTION

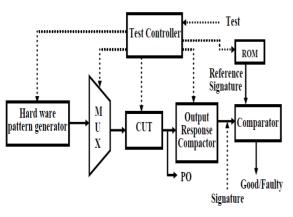

BIST is a design-for-testability technique that places the testing functions physically with the circuit under test (CUT), as illustrated in Figure 1. The basic BIST architecture requires the addition of three hardware blocks to a digital circuit: a test pattern generator, a response analyzer, and a check controller. The test pattern generator generates the test patterns for the CUT. Example of pattern generators are a ROM with stored patterns, counter and a linear feedback shift register (LFSR). A typical reply analyzer is a comparator with stored responses or an LFSR used as a signature analyzer. It a compacts and analyzes the test responses to conclude exactness of CUT. A test control block is necessary to activate the test and analyze the responses. However, in general, some test-related functions can be executed through a test controller circuit.

As shown in Figure 1, the wires from primary inputs (PIs) to MUX and wires from circuit output to primary outputs (POs) cannot be tested by BIST. In regular operation, the CUT

receive its inputs from other modules and performs the function for which it was designed. During test mode, a test pattern generator circuit applies a sequence of test patterns to the CUT and the test response are evaluated by a output response compactor. In the most common type of BIST, test responses are compacted in output response compactor to form (fault) signatures. The response signatures are compare with reference golden signatures generated or stored on-chip, and the error signal indicates whether chip is good or faulty.

Four primary parameters must be considered in developing a BIST methodology for embedded systems; these correspond with the design parameters for on-line testing techniques discussed.

Fault coverage: This is the fraction of faults of interest that can be exposed by the test patterns produced by pattern generator and detected by output response monitor. In presence of input bit stream errors there is a chance that the computed signature matches the golden signature, and the circuit is reported as fault free. This undesirable property is called masking or aliasing.

Test set size: This is the number of test patterns produced by the test generator, and is closely linked to fault coverage: generally, large test sets imply high fault coverage.

Hardware overhead: The extra hardware required for BIST is considered to be overhead. In most embedded systems, high hardware overhead is not acceptable.

Performance overhead: This refers to the impact of BIST hardware on normal circuit performance such as its worst-case (critical) path delays. Overhead of this type is sometimes more important than hardware overhead.

## II. BLOCK DIAGRAM OF BIST

Figure 1 Block diagram of BIST

BIST can be used for non-concurrent, on-line testing of the logic and memory parts of a system [2]. It can readily be configured for event-triggered testing, in which case, the BIST control can be tied to the system reset so that testing occurs during system start-up or shut down. BIST can also be designed for periodic testing with low fault latency. This requires incorporating a testing process into the CUT that guarantees the detection of all target faults within a fixed time.

On-line BIST is usually implemented with the twin goals of complete fault coverage and low fault latency. Hence, the test generation (TG) and response monitor (RM) are generally designed to guarantee coverage of specific fault models, minimum hardware overhead, and reasonable set size. These goals are met by different techniques in different parts of the system.

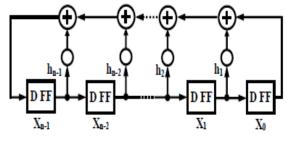

TG and RM are often implemented by easy, counter-like circuits, especially linear-feedback shift registers (LFSRs). The LFSR is simply a shift register formed from standard flipflops, with the outputs of selected flip-flops being fed back to the shift register's inputs. When used as a TG, an LFSR is set to cycle rapidly through a large number of its states. These states, whose choice and order depend on the design parameters of the LFSR, define the test patterns. In this mode of operation, an LFSR is seen as a source of (pseudo) random tests that are, in principle, applicable to any fault and circuit types. An LFSR can also serve as an RM by counting (in a special sense) the responses produced by the tests. An LFSR RM's final contents after applying a sequence of test responses forms a fault signature, which can be compared to a known or generated good signature, to observe if a fault is present. Ensuring that the fault coverage is sufficiently high and the number of tests is sufficiently low are the main problems through random BIST method. Two general approaches have been proposed to preserve the cost advantages of LFSRs while making the generated test sequence much shorter. Test points can be inserted in the CUT to improve controllability and observability; however, they can also result in performance loss. Alternatively, some determinism can be introduced into the generated test sequence, for example, by inserting specific "seed" tests that are known to detect hard faults.

A typical BIST architecture using LFSR is shown in Figure 2. Since the output patterns of the LFSR are time-shifted and repeated, they become correlated; this reduces the effectiveness of the fault detection. Therefore a phase shifter (a network of XOR gates) is often used to de-correlate the output patterns of the LFSR. The response of the CUT is usually compacted by a multiple input shift register (MISR) to a small signature, which is compared with a known fault-free signature to determine whether the CUT is faulty.

#### Pseudo-Random Pattern Generation

A string of 0's and 1's is called a pseudo-random binary sequence when the bits appear to be random in the local sense, but they are in some way repeatable. The linear feedback shift register (LFSR) pattern generator is most commonly used for pseudo-random pattern generation. In general, this requires more patterns than deterministic ATPG, but less than the exhaustive test. In contrast with other method, pseudo-random pattern BIST might require a long test time and necessitate evaluation of fault coverage by fault simulation. This pattern type, however, has the potential for lower hardware and performance overheads and less design effort than the prior methods. In pseudorandom test patterns, each bit has an approximately equal probability of being a 0 or a 1. The quantity of patterns applied is typically of the order of 103 to 107 and is related to the circuit's testability and the fault coverage required.

Linear feedback shift register reseeding is an example of a BIST technique that is based on controlling the LFSR state. LFSR reseeding might be static that is LFSR stops generating patterns while loading seeds, or dynamic, so as to is, test generation and seed loading can proceed simultaneously. The length of the seed can be any equal to the size of the LFSR (full reseeding) or less than the LFSR (partial reseeding). In [5], a dynamic reseeding technique that allows partial reseeding is proposed to encode test vectors. A set of linear equations is solved to obtain the seeds, and test vectors are ordered to facilitate the solution of this set of linear equations.

Figure 2 Standard LFSR circuit

## COMBINATIONAL BENCHMARK CIRCUIT C432

Several Industry standard benchmark circuits such as ISCAS-85, ISCAS-89, etc can be used to test latest design, test and manufacturing approaches and technologies. Following is a brief explanation of one of the ISCAS-85 circuits used for the purpose of testing the new low power pattern generation system described above.

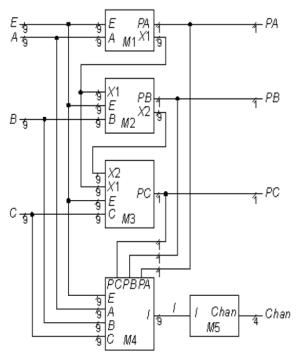

C432 is a 27-channel interrupt controller. The input channels are grouped into three 9-bit buses (we call them A, B and C), wherever the bit position within each bus determines the interrupt request priority. A forth 9-bit input (called E) enables and disables interrupt requests inside the respective bit positions. Figure below shows the c432 circuit. Figures show below the logic of the underlying modules.

Figure 3 C432 Combinational Circuits

• Logic Gates are in use at Primary input combination in  $(2^{3}6)$ .

Statistics: 36 inputs, 7 outputs, 160 gates, bus translations

Function: c432 is a 27-channel interrupt controller. The enter channels are group into three 9-bit buses (we name them A, B and C), where the bit arrangement within each bus determines the interrupt request priority. A forth 9-bit input (called E) enables and disables interrupt requests within the particular bit positions. The figure above concisely represents the circuit. The figure above shown contains the modules labeled M1, M2, M3, M4, and M5, which contain the underlying logic.

Comparison of Test Generation Strategies

Implementing a BIST strategy, the main issues are fault coverage, hardware overhead, test time overhead, and design effort. These four issues have very complicated relationship. Table 1 summarizes the characteristics of the test strategies mentioned earlier based on the four issues.

| Test Generation<br>Methodology | Fault<br>Coverage | Hardware<br>Overhead | Test Time<br>Overhead | Design<br>Effort        |  |  |

|--------------------------------|-------------------|----------------------|-----------------------|-------------------------|--|--|

| Stored Pattern                 | High              | High                 | Short                 | Large                   |  |  |

| Exhaustive                     | High              | Low                  | Long                  | Small<br>Large<br>Small |  |  |

| Pseudo-exhaustive              | High              | High                 | Medium                |                         |  |  |

| Pseudo-random                  | Low               | Low                  | Long                  |                         |  |  |

| Weighted Pseudo-random         | Medium            | Medium               | Long                  | Medium                  |  |  |

TABLE 1 COMPARISON OF DIFFERENT TEST STRATEGIES

BIST Response Compression/Compaction Techniques

During BIST, large amount of data in CUT responses are applied to Response Monitor (RM). For example, if we consider a circuit of 200 outputs and if we want to generate 5 million random patterns, then the CUT response to RM will be 1 billion bits. This is not manageable in practice. So it is necessary to compact this enormous amount of circuit responses to a manageable size that can be stored on the chip. The response analyzer compresses a very long test response into a single word. Such a word is called a signature. The signature is then compared with the pre-stored golden signature obtained from the fault-free responses using the same compression mechanism. If the signature matches the golden copy, the CUT is regard fault-free. Otherwise, it is faulty. There are different response analysis methods such as ones count, transition count, syndrome count, and signature analysis.

### III. RESULT ANALYIS

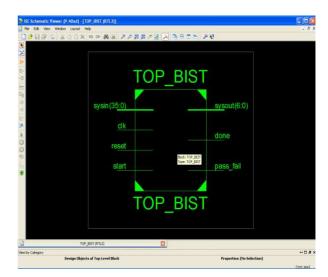

## **Block diagram**

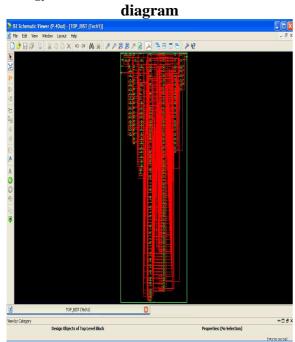

# **RTL** schematic

|             | Vindow Layout Help |                                     |                   |              |                    | -  |

|-------------|--------------------|-------------------------------------|-------------------|--------------|--------------------|----|

| 080         | 800×0              | a War + +                           | 88/323            | 0.9 1 18     |                    |    |

|             |                    |                                     |                   |              |                    |    |

|             |                    |                                     | TOP_BIST.1        |              |                    |    |

|             |                    | LFSR                                | IW                | RS_latch     |                    |    |

|             |                    |                                     | start, NV, 61, of |              |                    |    |

|             | -                  |                                     |                   | BIST_status  |                    |    |

|             |                    |                                     |                   |              |                    |    |

|             |                    |                                     |                   |              |                    |    |

|             |                    |                                     | N bit counter     | comparativ   |                    |    |

|             |                    | Block: TOP_BIST<br>Type: TOP_BIST:1 |                   |              |                    |    |

|             |                    | Wpe: TOP_BIST.1                     | ONTR              | CMPTR        |                    |    |

|             |                    |                                     |                   |              |                    |    |

|             |                    |                                     | ROM_UNIT          | c432         |                    |    |

|             |                    |                                     |                   |              |                    |    |

|             |                    |                                     | ROILU             | comb         |                    |    |

|             |                    |                                     | isdation_Unit     |              |                    |    |

|             | -                  |                                     | Subort Colle      |              |                    |    |

|             |                    |                                     |                   |              |                    |    |

|             |                    |                                     | 180_U             |              |                    |    |

|             |                    |                                     | TOP_BIST          |              | -                  |    |

|             |                    |                                     |                   |              |                    |    |

|             |                    |                                     |                   |              |                    |    |

|             | TOP_BIST           | r (RTL2)                            | 8                 |              |                    |    |

| by Category | Design Objects of  | (You have before be                 |                   | Bussetiar of | Instance: TOP_BIST | +0 |

# **Design summary**

|   | 🔊 🖬 🕼 😓 🐰 🗋 🗟 🗶 40                                                                                                                                            | A PPBBP                       |                                                    |                  |                       |                       |            |             |             |             |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------|------------------|-----------------------|-----------------------|------------|-------------|-------------|-------------|

| 6 | Sumary                                                                                                                                                        | -                             | TOP_BIST_TB Project Status (06/28/2014 - 15:35:25) |                  |                       |                       |            |             |             |             |

| 3 | - D TOB Properties                                                                                                                                            | Project File:                 | ExtensionBist4GIET.vise Parser E                   |                  |                       |                       | No Errors  |             |             |             |

| ð | Tring Constraints                                                                                                                                             | Module Name:                  | TOP_BEST                                           |                  | Implem                | Implementation State: |            | Synthesized |             |             |

| 5 | - 📋 Pinout Report                                                                                                                                             | Target Device:                | <mark>rget Device:</mark> xc7a100t-3csg            |                  | •Errors:              |                       |            | No Errors   |             |             |

|   | — 💭 Clock Report                                                                                                                                              | Product Version:              | ISE 14.3                                           |                  | • Warnings:           |                       |            | 2.Warr      | ings (2 new | <u>a</u>    |

| 8 | - 🙆 Static Timing<br>- Errors and Warnings                                                                                                                    | Design Goal:                  | Balanced                                           |                  | •Routing Results:     |                       |            |             |             |             |

|   | Parser Messages                                                                                                                                               | Design Strategy:              | Xiirx Default (                                    | unlocked)        | • Timing Constraints: |                       |            |             |             |             |

| 4 | - 📔 Synthesis Messages                                                                                                                                        | Environment:                  | System Settin                                      | ž.               | ۰F                    | inal Timing           | Score:     |             |             |             |

| 2 |                                                                                                                                                               |                               |                                                    | -                | -                     |                       |            |             |             |             |

|   | - 🗋 Place and Route Messages                                                                                                                                  | -                             | Device                                             | Itilization Summ | ary (estima           | ted values)           |            |             |             | · · · · · · |

|   | Timing Messages Bitgen Messages                                                                                                                               | Logic Utilization             | benee a                                            | Used             | ary (escina           | Available             |            | Utilizatio  | 1           | -           |

|   | Al Inplementation Messages                                                                                                                                    | Number of Slice Registers     |                                                    |                  | 40                    |                       | 126800     |             |             | 0           |

| E | Detailed Reports Synthesis Report                                                                                                                             | Number of Sike LUTs           |                                                    |                  | 151                   | 63400                 |            |             |             | 0           |

|   | - 🚺 Translation Report                                                                                                                                        | Number of fully used LUT-FF p | airs                                               |                  | 40                    |                       | 151        | 1           |             | 26          |

|   | - 🗋 Map Report                                                                                                                                                |                               | Number of bonded IOBs                              |                  | 48                    | 210                   |            | 1 22        |             |             |

|   | Place and Route Report Post-PAR Static Timing Report                                                                                                          | Number of BUFG/BUFGCTRLs      |                                                    |                  | í.                    |                       |            |             |             |             |

|   | Power Report Repen Report Repen Report Secondary Reports  Design Properties Conduct Report Report Conduct Report Report Source Code Report Source Code Report |                               |                                                    |                  |                       |                       |            |             |             |             |

|   |                                                                                                                                                               | v                             |                                                    | Detailed         | Reports               |                       |            |             |             | [           |

|   |                                                                                                                                                               | Report Name                   | Status                                             | Generated        |                       | Errors                | Warnings   |             | Infos       |             |

|   |                                                                                                                                                               | Synthesis Report              | Current                                            | Sat Jun 28 15:3  | 5:24 2014             | 0                     | 2 Warnings | (2 пен)     | 1 Info (1   | new)        |

|   |                                                                                                                                                               | Translation Report            |                                                    |                  |                       |                       | _          |             |             |             |

|   | Show Failing Constraints Show Warnings                                                                                                                        | Map Report                    | _                                                  |                  |                       |                       |            |             | -           |             |

|   | Show Errors                                                                                                                                                   | Place and Route Report        | -                                                  |                  |                       | -                     |            |             |             |             |

|   |                                                                                                                                                               | Power Report                  |                                                    | -                |                       | -                     | -          |             | -           |             |

|   |                                                                                                                                                               | Post-PAR Static Timing Report | -                                                  |                  |                       |                       |            |             |             |             |

|   |                                                                                                                                                               |                               |                                                    |                  |                       |                       | _          |             | -           |             |

|   |                                                                                                                                                               | Bitgen Report                 | _                                                  |                  |                       |                       |            |             |             |             |

|   |                                                                                                                                                               |                               |                                                    |                  |                       |                       |            |             |             |             |

|   |                                                                                                                                                               |                               |                                                    |                  |                       |                       |            |             |             |             |

## **Technology schematic**

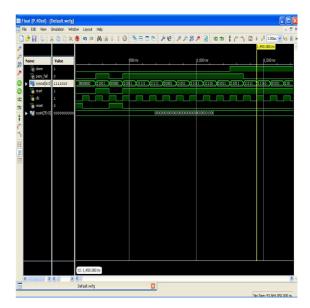

## **Output** waveform

## IV. CONCLUSION

The propose method implemented to test one of the combinational circuit by using Built in self test circuit. The presence of delay-inducing defects is causing increasing concern in the semiconductor industry today. To test used for such delay-inducing defects, scan-based transition fault testing techniques are being implemented. To Full scanning Process will Generated and then Fault coverage for Broadside testing is 80%, functional broadside testing is 40% and pseudorandom testing is 80%. Maximum length of testing full scan circuit is 402. Scanning percentage is 97%. Testing time for partial scan process is reduces Maximum testing length is reduced at 284.Here we were test the ISCAS-85 C432 27benchmark interrupt controller by using BIST circuit.

### REFERENCES

- J. Rearick, "Too much delay fault coverage is a bad thing," in Proc. Int.Test Conf., Oct. 2001, pp. 624–633.

- [2] J. Saxena, K. M. Butler, V. B. Jayaram, S. Kundu, N. V. Arvind, P.Sreeprakash, and M. Hachinger, "A case study of IR-drop in structuredat-speed testing," in Proc. Int. Test Conf., 2003, pp. 1098– 1104.

- [3] Pomeranz, "On the generation of scanbased test sets with reachablestates for testing under functional operation conditions," in Proc. Des. Autom. Conf., Jun. 2004, pp. 928–933.

- [4] Y.-C Lin, F. Lu, K. Yang, and K.-TCheng, "Constraint extraction forpseudofunctional scan-based delay testing," in Proc.Asia South Pacific Des. Autom. Conf., Jan.2005, pp. 166–171.

- [5] Z. Zhang, S. M. Reddy, and I.Pomeranz, "On generating pseudofunctionaldelay fault tests for scan designs," in Proc. Int.Symp. Defect Fault Toler. VLSI Syst., Oct.2005, pp. 398–405.

- [6] Pomeranz and S. M. Reddy, "Generation of functional broadside tests fortransition faults," IEEE Trans. Comput.-AidedDes. Integr. Circuits Syst., vol. 25, no. 10, pp.2207–2218, Oct.

- [7] Y.-C. Lin, F. Lu, K. Yang, and K.-T. Cheng, "Constraint extraction for pseudo-functional scan-based delay testing," in Proc. Asia South Pacific Design Autom. Conf., 2005, pp. 166–171.

- [8] Z. Zhang, S.M. Reddy, and I. Pomeranz, "On generating pseudofunctional delay fault tests for scan designs," in Proc. Int. Symp. Defect Fault Toler. VLSI Syst., 2005, pp. 398–405.

- [9] I. Polian and F. Fujiwara, "Functional constraints vs. test compression in scan-based delay testing," in Proc. Design, Autom. Test Euro. Conf., 2006, pp. 1–6.

- [10] M. Syal et al., "Astudy of implication based pseudo functional testing," in Proc. Int. Test Conf., 2006, pp. 1–10.

- [11] A. Jas, Y.-S. Chan, andY.-S. Chang, "An approach tominimizing functional constraints," in Proc. Defect Fault Toler. VLSI Syst., 2006, pp. 215–226.

- [12] H. Lee, I. Pomeranz, and S. M. Reddy, "On complete functional broadside tests for transition faults," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., pp. 583–587, 2008.

- [13] I. Pomeranz and S. M. Reddy, "On reset based functional broadside tests," in Proc. Design Autom. Test Euro. Conf., 2010, pp. 1438–1443.

- [14] H. Lee, I. Pomeranz, and S.M. Reddy, "Scan BIST targeting transition faults using a Markov source," in Proc. Int. Symp. Quality Electron. Design, 2004, pp. 497–502.

- [15] V. Gherman, H.-J. Wunderlich, J. Schloeffel, and M. Garbers, "Deterministic logic BIST for transition fault testing," in Proc. Euro. Test Symp., 2006, pp. 123–130.

- [16] Y.-C. Lin, F. Lu, and K.-T. Cheng, "Pseudofunctional testing," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., pp. 1535–1546, 2006.

- [17] M. Abramovici, M. A. Breuer, and A. D. Friedman, Digital Systems Testing and Testable Design. Piscataway, NJ: IEEE Press, 1995.

- [18] I. Pomeranz and S. M. Reddy, "Primary input vectors to avoid in random test sequences for synchronous sequential circuits," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., pp. 193–197, 2008.

- [19] I. Pomeranz, "Built-in generation of functional broadside tests," presented at the Design Autom. Test Euro. Conf., Grenoble, France, 2011.

- [20] P. H. Bardell, W. H. McAnney, and J. Savir, Built-In Test for VLSI. New York: Wiley, 1987.

- [21] B. Konemann, "LFSR-coded test patterns for scan designs," in Proc. Euro. Test Conf., 1991, pp. 237–242.