# DESIGN OF SINGLE PHASE SEVEN LEVEL PV INVERTER USING FPGA

S.Murugesan

Assistant Professor in Electrical and Electronics Engineering M.Kumarasamy College of Engineering, Karur murugesans.eee@mkce.ac.in

Abstract—This paper proposes an implementation of single phase seven level grid connected inverter for photovoltaic systems by using FPGA based pulse width modulated control process. Three types of reference signals that are identical to each other with an offset that is equivalent to the amplitude of the triangular carrier were used to generate the PWM signals. The inverter is able to produce seven levels of output voltage levels ( $V_{dc}$ ,  $2V_{dc}/3$ ,  $V_{dc}/3$ , 0, - $V_{dc}$ ,  $-2V_{dc}/3$ ,  $-V_{dc}/3$ ,  $V_{dc}/3$ ) from the dc supply voltage. A digital PI current control algorithm was implemented in a Xilinx XC3S250E FPGA to keep the current injected into the grid as sinusoidal. The proposed system was designed and verified through simulation and implemented in a prototype.

Key words: Grid Connected, Modulation index, Multi level inverter, Photo Voltaic (PV) system, Pulse Width modulation (PWM), Total harmonic distortion (THD).

#### I. INTRODUCTION

The ever increasing energy consumption, fossil fuels, soaring costs and exhaustible nature, and worsening environment have created a booming interest in renewable energy generation systems, one of which is photovoltaic. Such a system generates electricity by converting the sun's energy directly into electricity. Energy generated by photovoltaic system and can be delivered to power system networks through grid connected inverters.

A single-phase grid-connected inverter is usually used for residential or low-power applications of power ranges that are less than 10 kW [1]. Types of single-phase grid-connected inverters have been investigated [2]. A common topology of this inverter is full bridge three-level. The three level inverter should the satisfy specifications through its very high switching, but it may be unfortunately increase switching losses, acoustic noise, and level of interference to other equipment. By improving its output waveform reduces its harmonic content and hence, also the size of the filter used and the level of electromagnetic interference (EMI) generated by the inverter's switching operation [3].

Multilevel inverters are guaranteed that they have nearly

#### R.Senthilkumar

Assiatant Professor of Electrical and Electronics Engineering M.Kumarasamy College of Engineering, Karur Senthilkumarr.eee@mkce.ac.in

that are lower than those of conventional two-level inverters, a smaller filter size, and lower EMI, all of which make them cheaper, lighter, and more compact [3], [4].Various topologies for multilevel inverters have been pro- posed over the years. Common ones are diode-clamped [5]– [7], flying capacitor or multicell, cascaded H-bridge, and modified H-bridge multilevel.

This paper recounts the development of a novel modified H-bridge single-phase multilevel inverter that has two diode embedded bidirectional switches and a novel pulse width- modulated (PWM) technique. The designed topology was applied to a grid-connected photovoltaic system with considerations for a maximum-power-point tracker (MPPT) and a current-control algorithm.

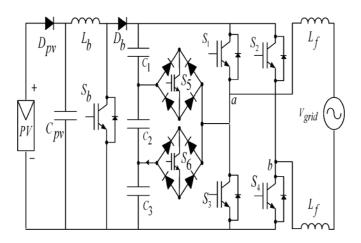

Fig.1. Proposed single phase seven level grid connected PV inverter

A multilevel power converter structure has been introduced as an alternative in high power and medium power situations. A multilevel converter not only assures high power ratings, but also enables the ease of usage for renewable energy sources such as photovoltaic, fuel cells and wind, can be easily interfaced to a multilevel converter system for a high power application.

The term multilevel begun with the three level, subsequently, several multilevel converter topologies has been developed over the years. However, the elementary concept of a multilevel converter to achieve higher power is to use a series power semiconductor switches with several lower voltage DC

sources to perform the power conversion by synthesizing a staircase voltage waveform. Batteries, Capacitors, and renewable energy voltage sources can be used as the multiple DC sources in order to achieve high voltage at the output; however, the calculated rated voltage of the power semiconductor switches depends only upon the rating of the DC voltage sources to which they are connected.

A multilevel converter gives more advantages over a conventional three level inverter that uses high switching frequency pulse width modulation (PWM).

#### II. PROPOSED INVERTER

The circuit diagram for PV connected single phase seven level grid connected inverter shown in fig. 3.2. Photovoltaic arrays were connected to the inverter via a dc-dc boost converter. The power generated by the inverter is to be delivered to the power network, so the utility to grid, rather than a load, was used. The dc-dc boost converter was required because the PV arrays had a voltage that is lower than the grid voltage. High dc bus voltages make more importance to ensure that power flows from the PV arrays to the grid. A filtering inductance Lf was used to filter the current injected into the grid. Proper switching of the inverter can produce seven outputvoltage lev- els ( $V_{dc}$ ,  $2V_{dc}$ /3,  $V_{dc}$ /3, 0,  $-V_{dc}$ ,  $-2V_{dc}$ /3,  $-V_{dc}$ /3) from the dc supply voltage.

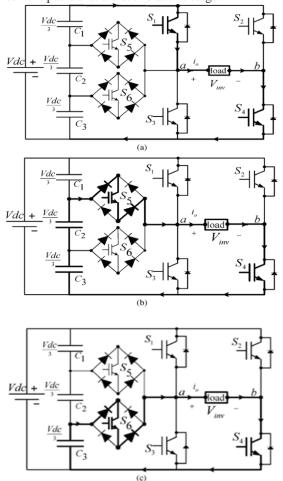

The proposed inverter's operation can be divided into seven switching states, they are shown in Fig. 2(a)to 2(g). Fig. 2(a), (d), and (g) shows a conventional inverter's operational states in sequence, while Fig. 2(b), (c), (e), and (f) shows additional states in the proposed inverter synthesizing one- and two-third levels of the dc-bus voltage. The required seven levels of output voltage were generated as follows

- 1) Maximum positive output  $(V_{dc})$ : When  $S_1$  is ON state, connecting the load positive terminal to  $V_{dc}$ , and  $S_4$  is ON, con- necting the load negative terminal to ground. Remaining controlled switches are OFF; the voltage applied to the load terminals is  $V_{dc}$ . Fig. 2(a) shows the current paths that are active at this stage.

- 2) Two-third positive output (2V<sub>dc</sub> ∕3): The bidirectional switch S<sub>5</sub> is ON state, connecting the load positive terminal, and S<sub>4</sub> is ON, connecting the load negative terminal to ground. Remaining controlled switches are OFF; the voltage applied to the load terminals is 2V<sub>dc</sub> ∕3. Fig. 2(b) shows the current paths that are active at this stage.

- 3) One-third positive output  $(V_{dc} / 3)$ : The bidirectional switch  $S_6$  is ON state, connecting the load positive terminal, and  $S_4$  is ON, connecting the load negative terminal to ground. Remaining controlled switches are OFF; the voltage applied to the load terminals is  $V_{dc} / 3$ . Fig. 2(c) shows the current paths that are active at this stage.

- 4) Zero output: This level can be produced by two switching combinations; switches  $S_3$  and  $S_4$  are ON, or  $S_1$  and  $S_2$  are ON state, and remaining controlled switches are OFF; terminal *ab* is a short circuit level and the voltage applied to the load terminals is zero. Fig. 2(d) shows the current paths that are active at this stage.

- 5) One-third negative output  $(-V_{dc}/3)$ : The bidirectional switch  $S_5$  is ON state, connecting the load positive terminal, and  $S_2$  is ON, connecting the load negative terminal to  $V_{dc}$ . Remaining switches are OFF; the voltage applied to the load terminals is  $-V_{dc}/3$ . Fig. 2(e) shows the current paths that are active at this stage.

- 6) Two-third negative output (-2V<sub>dc</sub> ∕3): The bidirectional switch S<sub>6</sub> is ON, connecting the load in positive terminal, and S<sub>2</sub> is ON, connecting the load negative terminal to ground. Remaining controlled switches are OFF; the voltage applied to the load terminals is -2V<sub>dc</sub> ∕3. Fig. 2(f) shows the current paths that are active at this stage.

- 7) Maximum negative output  $(-V_{dc})$ : When  $S_2$  is ONstate, connecting the load negative terminal to  $V_{dc}$ , and  $S_3$  is ON, con- necting the load positive terminal to ground. Remaining controlled switches are OFF; the voltage applied to the load terminals is  $-V_{dc}$ . Fig. 2(g) shows the current paths that are active at this stage.

Table I shows the switching combinations that generated the seven output-voltage levels  $(0, -V_{dc}, -2V_{dc})$ ,  $/3, -V_{dc}$ ,  $/3, V_{dc}$ ,  $2V_{dc}$ ,  $/3, V_{dc}$ , /3). TABLE I

OUTPUT VOLTAGE ACCORDING TO THE SWITCHES' ON–OFF CONDITION

| $v_0$               | S <sub>1</sub> | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | S5  | S <sub>6</sub> |

|---------------------|----------------|----------------|----------------|----------------|-----|----------------|

| V <sub>dc</sub>     | on             | off            | off            | on             | off | off            |

| 2V <sub>dc</sub> /3 | off            | off            | off            | on             | on  | off            |

| V <sub>dc</sub> /3  | off            | off            | off            | on             | off | on             |

| 0                   | off            | off            | on             | on             | off | off            |

| 0*                  | on             | on             | off            | off            | off | off            |

| -V <sub>dc</sub> /3 | off            | on             | off            | off            | on  | off            |

| $-2V_{dc}/3$        | off            | on             | off            | off            | off | on             |

| -V <sub>dc</sub>    | off            | on             | on             | off            | off | off            |

#### **III. PWM TECHNIQUES**

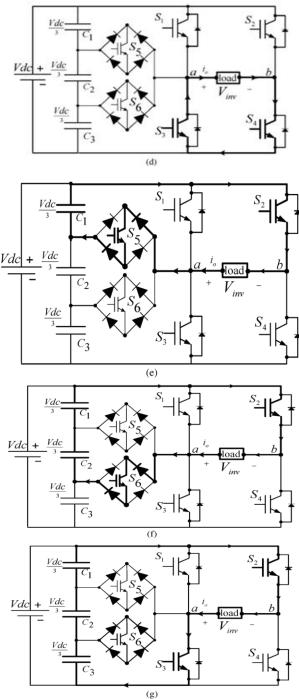

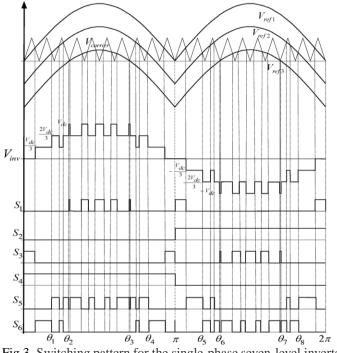

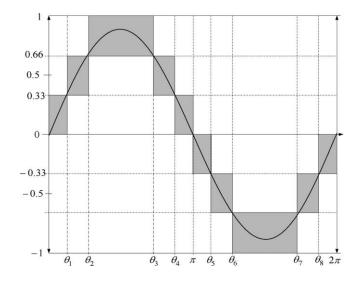

A novel PWM modulation technique was introduced to generate the PWM switching signals. Three reference signals (Vref1, Vref2, and Vref3) were compared with a carrier signal (Vcarrier). The corresponding reference signals had the same frequency, amplitude and were in phase with an offset value that was equivalent to the amplitude of the carrier signal. The reference signals were each compared with the carrier signal. When the value of  $V_{ref1}$ had exceeded the peak amplitude of Vcarrier, Vref2 is made the comparison with Vcarrier until it had exceeded the peak amplitude of Vcarrier. Then, onward, Vref3 would take charge and would be compared with Vcarrier until it makes the value which is reached to zero. Once  $V_{ref3}$  had reached zero, the value of  $V_{ref2}$  would be compared until it reached zero. After that moment Vref1 would be compared with Vcarrier. Fig. 3 shows the result of switching pattern. The switches S1, S3, S5, and S6 would be switching at the rate of the carrier signal frequency, whereas S2 and S4 would operate at a frequency that was equivalent to the fundamental frequency.

For one cycle of the fundamental frequency, the proposed inverter operated through six modes. Fig. 4 shows the perunit output-voltage signal for one cycle. The six modes are described as follows:

> Mode 1 :  $0 < \omega t < \theta_1$  and  $\theta_4 < \omega t < \pi$ Mode 2 :  $\theta_1 < \omega t < \theta_2$  and  $\theta_3 < \omega t < \theta_4$ Mode 3 :  $\theta_2 < \omega t < \theta_3$ Mode 4 :  $\pi < \omega t < \theta_5$  and  $\theta_8 < \omega t < 2\pi$ Mode 5 :  $\theta_5 < \omega t < \theta_6$  and  $\theta_7 < \omega t < \theta_8$ Mode 6 :  $\theta_6 < \omega t < \theta_7$ .....(1)

Fig.3. Switching pattern for the single-phase seven-level inverter.

Fig.4. Seven-level output voltage ( $V_{ab}$ ) and switching angles. The phase angle of the device depends on the modulation index  $M_a$  Theoretically the modulation index is

$$M_{a} = \frac{A_{m}}{A_{c}}$$

(2)

For single reference signal and dual carrier signal the modulation signal defined to be [6]

$$M_{a} = \frac{A_{m}}{2A_{c}}$$

(3)

The proposed inverter uses the three carrier signal so the modulation index is defined as

Where  $A_c$  is the peak to peak value of the carrier signal and  $A_m$  is the peak to peak value of the voltage reference signal  $V_{ref.}$

When the modulation intex more than 0.33 and less than 0.66. The phase angle displacement is given by

#### IV. CONTROL SYSTEM

FPGA is Programmable Logic Device developed by one of the vital vendor of VLSI that is Xilinx, Inc. It comprises of millions of logic gates. From that some of them combined together to form a Configurable Logic Block (CLB). CLB simplifies higher-level circuit design. Netlist of gates that means Gates interconnections using software are defined through SRAM or ROM. Thus it makes the flexibility modification in the designed circuit without altering the hardware part. When considering the Concurrent operation, it requires less hardware, easy and fast circuit modification, especially low cost for a complex circuitry and rapid prototyping make it as the most favorable choice for prototyping an ASIC.

The carrier wave is compared with the multiplied modulating signal which is derived from the look-up table. The corresponding data of the look up table are stored in the internal ROM unit. The external multiplicands and already stored data will determine the modulation index of the PWM. The data stored in the look-up table (ROM) consists of 60 data from the Red phase and another 60 data from the Blue phase. Most Part of Yellow phase is derived through addition of Red and Blue phases. Selector Unit and Multiplexer are used in the selection of required signal to the appropriate channel as to form a proper PWM output pattern at the output terminals.

The shifting of signal waveform is essential in order to vary the power factor of the system. The process is carried out by delay or advance the reset signal. The reset signal is fully connected to the entire module. A signal of positive triggering edge during positive and negative cycle is used as a reference by the reset signal. By producing the advancement and delay through reset signal by the external command will force the current in the main circuit to lead or lag the voltage supply.

## V. SIMULATION AND EXPERIMENTAL RESULTS A.SIMULATION RESULTS

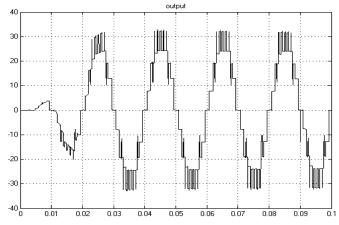

MATLAB SIMULINK simulated the proposed configuration before it was physically implemented in a prototype. The PWM switching patterns were generated by comparing three reference signals ( $V_{ref1}$ ,  $V_{ref2}$ , and  $V_{ref3}$ ) against a triangu-lar carrier signal (see Fig. 6). Subsequently, the comparing process produced PWM switching signals for switches  $S_1$  – $S_6$ , as Fig.5 and the output voltage of seven level inverter shown in fig.6

Fig.5. Simulation Output voltage of seven level inverter

One leg of the inverter operated at a high switching rate that was equivalent to the frequency of the carrier signal, while the other leg operated at the rate of the fundamental frequency (i.e., 50 Hz). Switches  $S_5$  and  $S_6$  also operated at the rate of the carrier signal.

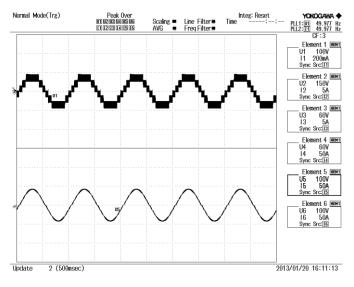

### **B.EXPERIMENTAL RESULTS**

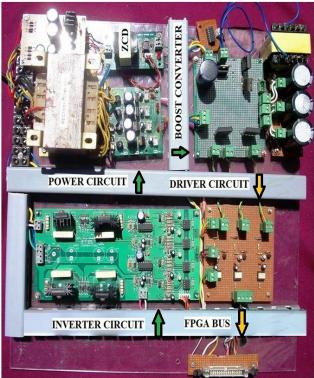

The hardware output voltage for single phase seven level inverter shown in fig.7 and hardware photocopy shown in fig.8.

Fig.6. Output voltage for single phase seven level inverter

Fig.7.Hardware Photocopy of proposed system. C.THD RESULT FOR MULTILEVEL INVERTER

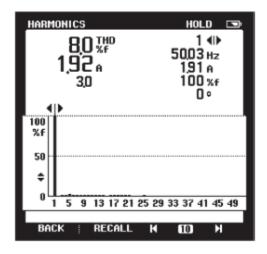

Fig.8. THD results for 3-level inverter

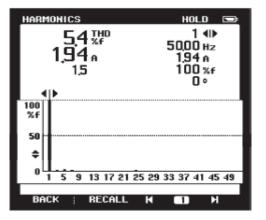

Fig.9. THD results for 5-level inverter

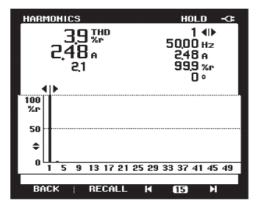

Fig.9. THD results for Proposed system

#### VI.CONCLUSION

Using Xilinx FPGA to generate the PWM provides flexibility to modify the designed circuit without altering the hardware part. When Concurrent operation is used, it requires less hardware, easy and fast circuit modification, especially low cost for a complex circuitry and rapid prototyping make it as the most favorable choice for the PWM generation. From the analysis of simulation and experimental results it is confirmed that the harmonic distortion of the output current waveform of the inverter fed to the grid is within the stipulated limits laid down by the utility companies, the THD is less than five and three level inverter. All the above advantages have made the inverter configuration highly suitable for grid connected photovoltaic application (5kW).

#### REFERENCES

- M. Calais and V. G. Agelidis, "Multilevel converters for single-phase grid connected photovoltaic systems—An overview," in Proc. IEEE Int. Symp.Ind. Electron., 1998, vol. 1, pp. 224–229.

- [2] S. B. Kjaer, J. K. Pedersen, and F. Blaabjerg, "A review of single-phase grid connected inverters for photovoltaic modules," IEEE Trans. Ind. Appl., vol. 41, no. 5, pp. 1292–1306, Sep./Oct. 2005.

- [3] P. K. Hinga, T. Ohnishi, and T. Suzuki, "A new PWM inverter for photovoltaic power generation system," in Conf. Rec. IEEE Power Electron. Spec. Conf., 1994, pp. 391–395.

- [4] Y. Cheng, C. Qian, M. L. Crow, S. Pekarek, and S. Atcitty, "A comparison of diode-clamped and cascaded multilevel converters for a STATCOM

with energy storage," IEEE Trans. Ind. Electron., vol. 53, no. 5, pp. 1512–1521, Oct. 2006.

- [5] M. Saeedifard, R. Iravani, and J. Pou, "A space vector modulation strategy for a back-to-back five-level HVDC converter system," IEEE Trans. Ind. Electron., vol. 56, no. 2, pp. 452–466, Feb. 2009.

- [6] S. Alepuz, S. Busquets-Monge, J. Bordonau, J. A.M. Velasco, C. A. Silva, J. Pontt, and J. Rodríguez, "Control strategies based on sym-metrical components for grid-connected converters under voltagedips," IEEE Trans. Ind. Electron., vol. 56, no. 6, pp. 2162–2173, Jun. 2009.

- [7] J. Rodríguez, J. S. Lai, and F. Z. Peng, "Multilevel inverters: A survey of topologies, controls, and applications," IEEE Trans. Ind. Electron., vol. 49, no. 4, pp. 724–738, Aug. 2002.

S.Murugesan has received B.E. degree in Electrical and Electronics Engineering in 2009 at JJ college of Engineering and Technology, Trichy, Tamilnadu, India. He received M.E degree in Power Electronics and Drives in 2013 at Sudharsan Engineering

College, Pudukkottai, Tamilnadu, India. He presented many international and national Conferences in many aspects. Currently he is working as an Assistant Professor in M.Kumarasamy College of Engineering, Karur His interest is in the field of Power Electronics, Power systems & Wireless protocol technologies.

He got UG degree from PSNA college of Engineering, Dindigul, Tamilnadu. He got PG degree from PSNA college of Engineering, Dindigul, Tamilnadu. He had attended more conferences and presented more reputed papers in the field of Power Electronics and Drives and currently he is

working as an Assistant Professor in M.Kumarasamy College of Engineering, Karur. His interest is in the field of Power electronics control, power system protection and control technologies.